# Source Current Harmonics Reduction with Improved Shunt Active Power Filter for Renwable Enrgey Source

U. Sai Kumar<sup>1</sup>, J. V. Pavan Chand<sup>2</sup>

EEE Department, LakiReddy Bali Reddy College of Engineering, Mylavaram.

**Abstract:** As humans have become more dependent on technology there is increase in power demand. To generate a pollution free power we are depending on renewable energy resources. In this paper we are using both solar energy and wind energy. A dynamic power filter actualized with a four-leg voltage-source inverter utilizing predictive control method has been used in this paper. The use of a four-leg voltage source inverter allows the compensation of current symphonies parts, and also uneven current created by single-phase nonlinear loads. A scientific model of the dynamic power filter, including the impact of the proportional power framework impedance, is inferred and used to outline the predictive control calculation. The proposed dynamic power filter and the related control plot under relentless state and transient working conditions is exhibited through reenactment's and trial comes about.

**Keywords:** Active power filter, current control, four-leg converters, prescient model

#### 1. Introduction

Electric utilities and end clients of electric power are ending up progressively worried about taking care of the developing vitality demand. Seventy five percent of aggregate worldwide vitality request is provided by the consuming of non-renewable energy sources. In any case, expanding air contamination, a dangerous atmospheric devation concerns, reducing non-renewable energy sources and their expanding cost have made it important to look towards inexhaustible sources as a future vitality arrangement. Since the previous decade, there has been a huge enthusiasm for some nations on sustainable power source for control age. The market advancement and government's motivating forces have additionally quickened the sustainable power source area development. Sustainable power source (RES) incorporated at circulation level is named as disseminated age (DG). The utility is worried because of the high entrance level of irregular RES in appropriation frameworks as it might represent a danger to arrange regarding dependability, voltage control and power-quality (PQ) issues. Accordingly, the DG frameworks are required to conform to strict specialized and administrative systems to guarantee sheltered, dependable and effective operation of general system. With the headway in control gadgets and advanced control innovation, the DG frameworks would now be able to be effectively controlled to upgrade the framework operation with enhanced PQ at PCC.

Be that as it may, the broad utilization of energy gadgets based gear and non-straight loads at PCC produce consonant streams, which may weaken the nature of energy [1], [2]. By and large, current controlled voltage source inverters are utilized to interface the irregular RES in conveyed framework. As of late, a couple of control methodologies for framework associated inverters consolidating PQ arrangement have been proposed. In [3] an inverter works as dynamic inductor at a specific recurrence to assimilate the symphonious current. Be that as it may, the correct figuring of system inductance progressively is troublesome and may crumble the control execution. A comparable approach in which a shunt dynamic channel goes about as dynamic conductance to moist out the music in circulation arrange is proposed in [4]. In [5], a control methodology for sustainable interfacing inverter in view of - hypothesis is proposed. In this system both load and inverter current detecting is required to remunerate the heap current sounds. The non-straight load current music may bring about voltage sounds and can make a genuine PQ issue in the power framework arrange. Dynamic power channels (APF) are widely used to repay the heap current sounds and load unbalance at dissemination level. This outcomes in an extra equipment cost. Be that as it may, in this paper creators have consolidated the highlights of APF in the, ordinary inverter interfacing inexhaustible with the network, with no extra equipment cost. Here, the principle thought is the greatest usage of inverter rating which is more often than not underutilized because of irregular nature of RES. It is appeared in this paper the framework interfacing inverter can successfully be used to perform following vital capacities: 1) exchange of dynamic power collected from the sustainable assets (wind, sun based, and so on.); 2) stack receptive power request bolster; 3) current sounds pay at PCC; and 4) current unbalance and impartial current pay if there should be an occurrence of 3-stage 4-wire framework. This paper displays the numerical model of the 4L-VSI and the standards of operation of the proposed prescient control plot, including the outline technique. The entire portrayal of the chose current

reference generator executed in the dynamic power channel is likewise introduced. At long last, the proposed dynamic power channel and the viability of the related control conspire pay are shown through re-enactment and approved with exploratory outcomes got in a 2kVA framework.

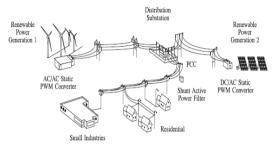

Fig. 1 Remain solitary Hybrid Power Generation System with a Shunt Active Power Filter.

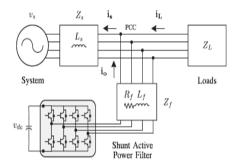

Fig .2. Three-Phase Equivalent Circuit of the proposed Shunt Active Power Filter.

## 2. Four-Leg Converter Model

Figure 1 demonstrates the arrangement of a run of the mill control appropriation framework with sustainable power age. It comprises of different sorts of energy age units and diverse sorts of burdens. Sustainable sources, for example, wind and daylight, are regularly used to produce power for private clients and little businesses. The two sorts of energy age utilize air conditioning/air conditioning and dc/air conditioning static PWM converters for voltage change and battery banks for long haul vitality stockpiling. These converters perform most extreme power guide following toward remove the greatest vitality conceivable from wind and sun. The electrical vitality utilization conduct is arbitrary and flighty, and in this way, it might be single-or three-stage, adjusted or lopsided, and straight or nonlinear. A dynamic power channel is associated in parallel at the purpose of regular coupling to repay current sounds, current unbalance, and responsive power. It is created by an electrolytic capacitor, a four-leg PWM converter, and a first-arrange yield swell channel, as appeared in Figure 2. This circuit considers the power framework proportional impedance Zs, the converter yield swell channel impedanceZf, and the heap impedance ZL.

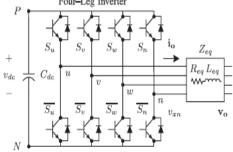

The four-leg PWM converter topology is appeared in Figure 3. This converter topology is like the traditional three-stage converter with the fourth leg associated with the impartial transport of the framework. The fourth leg builds changing states from 8 (2^3) to 16 (2^4), enhancing control adaptability and yield voltage quality, and is appropriate for current uneven pay.

Fig 3: Two-level four-leg PWM-VSI topology.

The voltage in any leg x of the converter, measured from the impartial point (n), can be communicated as far as exchanging states, as takes after:

$$v_{xn} = S_x - S_n v_{dc}$$

,  $x = u, v, w, n$  (1)

The numerical model of the channel got from the equal circuit appeared in Figure 2 is

$$V_0 = v_{xn} - R_{eq} i_o - L_{eq} \frac{di_o}{dt}$$

(2)

Where Req and Leq are the 4L-VSI yield parameters communicated as Thevenin impedances at the converter yield terminals Zeq. In this way, the Thevenin identical impedance is dictated by an arrangement association of the swell channel impedance  $Z_f$  and a parallel course of action between the framework comparable impedance  $Z_s$  and the heap impedance  $Z_L$ .

$$Z_{eq} = \frac{Z_s Z_l}{Z_s + Z_l} + z_f \approx Z_s + Z_f.$$

(3)

For this model, it is assumed that  $Z_L \approx Z_S$ , that the resistive part of the system's equivalent impedance is neglected, and that the series reactance is in the range of 3–7% p.u., which is an acceptable approximation of the real system. Finally in (2),

$$R_{eq} = R_f$$

and  $L_{eq} = L_s + L_f$ .

## 3. Digital Predictive Current Control

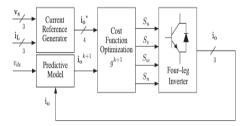

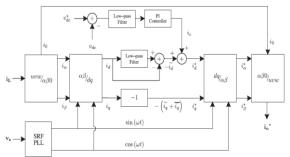

The piece outline of the proposed advanced prescient current control plot is appeared in Figure 4. This control conspire is fundamentally an improvement calculation and, accordingly, it must be actualized in a chip. Thusly, the examination must be created utilizing discrete science keeping in mind the end goal to consider extra confinements, for example, time postponements and approximations.

Fig 4: Proposed Predictive Digital Current Control Block Diagram

The fundamental normal for prescient control is the utilization of the framework model to foresee the future conduct of the factors to be controlled. The controller utilizes this data to choose the ideal exchanging state that will be connected to the power converter, as indicated by predefined advancement criteria. The prescient control calculation is anything but difficult to execute and to comprehend, and it can be actualized with three fundamental pieces, as appeared in Fig. 4.

- 1) Current Reference Generator: This unit is intended to produce the required current reference that is utilized to remunerate the bothersome load current parts. For this situation, the sys-tem voltages, the heap streams, and the dc-voltage converter are measured, while the impartial yield present and nonpartisan load current are created specifically from these signs (IV).

- 2) Prediction Model: The converter demonstrate is utilized to anticipate the yield converter current. Since the controller works in discrete time, both the controller and the framework display must be spoken to in a discrete time area [22]. The discrete time display comprises of a recursive framework condition that speaks to this forecast framework. This implies for a given testing time Ts, knowing the converter exchanging states and control factors at moment kTs, it is conceivable to anticipate the following states at any moment [k+1]Ts. Because of the principal arrange nature of the state conditions that depict the model in (1)– (2), an adequately precise first-arrange guess of the subsidiary is considered in this paper.

$$\frac{d_{x}}{d_{t}} \approx \frac{x \left[k+1\right] - x(k)}{T_{s}} \tag{4}$$

The 16 conceivable yield current anticipated esteems can be acquired from (2) and (4) as

$$i_o[k+1] = \frac{T_s}{L_{eq}} (v_{xn}(k) - v_o[k] + \left(1 - \frac{R_{eq}T_s}{L_{eq}}\right) i_o[k].$$

(5)

From (5), with a specific end goal to foresee the yield current io at the moment (k + 1), the info voltage esteem vo and the converter yield voltage vxN, are required. The calculation figures all 16 values related with the conceivable blends that the state factors can accomplish.

Cost Function Optimization: keeping in mind the end goal to choose the ideal exchanging state that must be connected to the power converter, the 16 anticipated esteems acquired for io[k + 1] are contrasted and the reference utilizing a cost work g, as takes after:

$$g[k+1] = (i_{ou}^*[k+1] - i_{ou}[k+1])^2 + (i_{ov}^*[k+1] - i_{ov}[k+1])^2 + (i_{ow}^*[k+1] - i_{ow}[k+1])^2 + (i_{ou}^*[k+1] - i_{ou}[k+1])^2 (6)$$

The yield current (io ) is equivalent to the reference (i\*o) when g = 0. In this way, the streamlining objective of the cost work is to accomplish a g esteem near zero. The voltage vector vx N that limits the cost work is picked and afterward connected at the following inspecting state. Amid each testing state, the exchanging state that produces the base estimation of g is chosen from the 16 conceivable capacity esteems. The calculation chooses the exchanging state that creates this negligible esteem and applies it to the converter amid the ss k+1 state.

# 4. Current Reference Generation

A dq-based current reference generator conspire is utilized to get the dynamic power channel current reference signals. This plan displays a quick and exact flag following ability. This trademark stays away from voltage vacillations that fall apart the present reference flag influencing pay execution [28]. The present reference signals are acquired from the relating load streams as appeared in Fig. 5. This module ascertains the reference flag streams required by the converter to remunerate receptive power, current symphonies, and current awkwardness. The removal control factor ( $\sin \phi_{(L)}$ ) and the most extreme aggregate symphoniescontortion of the heap (THD(L) characterizes the connection transports between the obvious power required by the dynamic power channel, regarding the heap, as appeared

$$\frac{S_{APF}}{S_l} = \frac{\sqrt{\sin\phi_L + THD_l^2}}{\sqrt{1 + THD_l^2}} \tag{7}$$

where the estimation of THD(L) incorporates the greatest compensable symphonies present, characterized as twofold the examining recurrence fs . The recurrence of the most extreme current symphonious segment that can be repaid is equivalent to one portion of the converter exchanging recurrence.

The dq-based plan works in a turning reference outline; in this way, the deliberate streams must be duplicated by the sin(wt) and cos(wt) signals. By utilizing dq-change, the d current part is synchronized with the relating stage to-unbiased framework voltage, and the q current segment is stage moved by 90°. The sin(wt) and cos(wt) synchronized reference signals are acquired from a synchronous reference outline (SRF) PLL [29]. The SRF-PLL produces an unadulterated sinusoidal waveform notwithstanding when the framework voltage is extremely twisted.

Fig. 5.dq-based current reference generator block diagram.

Following blunders are wiped out, since SRF-PLLs are intended to maintain a strategic distance from stage voltage unbalancing, sounds (i.e.,less than 5% and 3% in fifth and seventh, separately), and off-set caused by the nonlinear load conditions and estimation mistakes. Condition (8) demonstrates the connection between the genuine streams  $i_{Lx}(t)(x=u,v,w)$  and the related dq parts (id and iq)

$$\begin{bmatrix} i_d \\ i_q \end{bmatrix} = \sqrt{\frac{2}{3}} \begin{bmatrix} \sin \omega t & \cos \omega t \\ -\cos \omega t & \sin \omega t \end{bmatrix} \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \frac{\sqrt{3}}{2} & -\frac{\sqrt{3}}{2} \end{bmatrix} \begin{bmatrix} i_{Lu} \\ i_{Lv} \\ i_{L\omega} \end{bmatrix} (8)$$

A low-pass channel (LFP) separates the dc part of the stage streams  $i_d$  to create the symphonies reference components  $-i_d$ . The responsive reference segments of the stage ebbs and flows are acquired by stage moving the relating air conditioning and dc segments of iq by  $180^{\circ}$ . So as to keep the dc-voltage consistent, the plentifulness of the converter reference current must be changed by including a dynamic power reference flag ie with the d-segment, as will be clarified in Section IV-A. The subsequent signals  $i_d^*$  are changed back to a three-stage framework by applying the opposite Park and Clark change, as appeared in (9). The cutoff recurrence of the LPF utilized as a part of this paper is 20 Hz. The current that courses through the impartial of the heap is repaid by infusing the same momentary esteem acquired from the stage streams, stage moved by  $180^{\circ}$ , as appeared next

$$i_{on}^* = -(i_{Lu} + i_{Lv} + i_{Lw}) \tag{9}$$

One of the real favourable circumstances of the dq-based current reference generator plot is that it permits the usage of a straight controller in the dc-voltage control circle. In any case, one essential weakness of the dq-based current reference outline calculation used to create the present reference is that a moment arrange consonant part is produced in id and iq under unequal working conditions. The abundance of this symphonies relies upon the percent of unequal load current (communicated as the connection between the negative grouping current iL,2 and the positive arrangement current iL,1). The second-arrange consonant can't be expelled from id and iq, and in this manner produces a third symphonious in the reference current when it is changed over back to abc outline [31]. Fig. 6 demonstrates the percent of framework current unevenness and the percent of third symphonious framework current, in capacity of the percent of load current lopsidedness. Since the heap current does not have a third symphonious, the one produced by the dynamic power channel streams to the power framework.

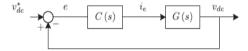

Fig: 6 DC voltage control block diagram

# A. DC-Voltage Control

The dc-voltage converter is controlled with a customary PI controller. This is an essential issue in the assessment, since the cost work (6) is composed utilizing just current references, with a specific end goal to maintain a strategic distance from the utilization of weighting factors. For the most part, these weighting factors are gotten tentatively, and they are not all around characterized when distinctive working conditions are required. Moreover, the moderate dynamic reaction of the voltage over the electrolytic capacitor does not influence the present transient reaction. Thus, the PI controller speaks to a basic and viable option for the dc-voltage control. The dc-voltage stays steady (with a base estimation of  $\sqrt{6} \, v_{s(rms)}$ ) until the point when the dynamic power consumed by the converter declines to a level where it can't make up for its misfortunes. The dynamic power consumed by the converter is controlled by changing the adequacy of the dynamic power reference flag i.e, which is in stage with each stage voltage. In the piece chart appeared in Fig. 5, the dc-voltagev<sub>dc</sub> is measured and after that contrasted and a consistent reference esteemv<sup>\*</sup><sub>dc</sub>. The mistake (e) is handled by a PI controller, with two additions, k<sub>p</sub> and T<sub>i</sub>. The two additions are computed by the dynamic reaction necessity. Fig. 6 demonstrates that the yield of the PI controller is encouraged to the dc-voltage exchange work Gs ,which is spoken to by a first-arrange framework (10)

$$G(s) = \frac{v_{dc}}{i_e} = \frac{3}{2} \frac{K_p \, v_s \sqrt{2}}{C_{dc} \, v_{dc}^*} (10)$$

The equivalent closed-loop transfer function of the given system with a PI controller (11) is shown in (12)

$$C(s) = K_p \left( 1 + \frac{1}{T_i \cdot s} \right)$$

(11)

Since the time response of the dc-voltage control loop does not need to be fast, a damping factor  $\zeta = 1$  and a natural angular speed  $\omega_n = 2\pi \cdot 100$  rad/s are used to obtain a critically damped response with minimal voltage oscillation. The corresponding integral time  $T_i = 1/a$  (13) and proportional gain  $K_P$  can be calculated a

$$\zeta = \sqrt{\frac{3}{8}} \frac{K_p \, v_s \sqrt{2T_i}}{C_{dc} \, v_{dc}^*} (13)$$

$$w_n = \sqrt{\frac{3}{2} \frac{K_p v_s \sqrt{2}}{C_{dc} v_{dc}^* T_i}} (14)$$

## TABLE-1 SPECIFICATION PARAMETERS

| S.No | Variables        | Description            | Value            |

|------|------------------|------------------------|------------------|

| 1    | $V_{\rm s}$      | Source voltage         | 415v             |

| 2    | f                | System frequency       | 50H <sub>Z</sub> |

| 3    | $V_{dC}$         | dc-voltage             | 162V             |

| 4    | $C_{dc}$         | dc-capacitor           | 2200 μF          |

| 5    | $L_{\rm f}$      | Filter inductor        | 5.0 mH           |

| 6    | $R_{\mathrm{f}}$ | Internal resistance    | $0.6\Omega$      |

|      |                  | with in L <sub>f</sub> |                  |

| 7    | $T_{\rm s}$      | Sampling time          | 20μs             |

| 8    | T <sub>e</sub>   | Execution time         | 16µs             |

## 5. Results Analysis

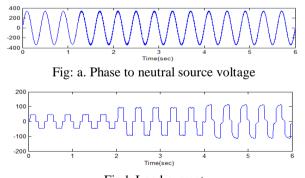

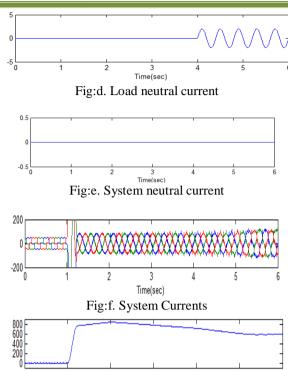

The active filter starts to compensate at  $t=t_1$ . At this time, the active power filter injects an output current  $i_{ou}$  to compensate current harmonic components, current unbalanced, and neutral current simultaneously. During compensation, the system currents  $i_s$  show sinusoidal waveform, with low total harmonic distortion (THD = 3.93%). At  $t=t_2$ , a three-phase balanced load step change is generated from 0.6 to 1.0 p.u. The compensated system currents remain sinusoidal despite the change in the load current magnitude. Finally, at  $t=t_3$ , a single-phase load step change is introduced in phase u from 1.0 to 1.3 p.u., which is equivalent to an 11% current imbalance. As expected on the load side, a neutral current flows through the neutral conductor  $i_{Ln}$  but on the source side, no neutral current is observed ( $i_{sn}$ ). Simulated results show that the proposed control scheme effectively eliminates unbalanced currents. Additionally, that the dc-voltage remainsstable throughout the whole active power filter operation.

Fig:b.Load current

Pig:b.Load current

Time(sec)

Fig:c. Active power filter output current

Time (sec)

Fig : g. DC voltage converter

#### 6. Conclusion

The utilization of a prescient control calculation for the converter current circle turned out to be a successful answer for dynamic power channel applications, enhancing current following capacity, and transient reaction. The prescient current control calculation is a steady and hearty arrangement. Re-enacted and test comes about have demonstrated the pay viability of the proposed dynamic power channel.

#### 7. Future Scope

For speed operation of the converter PI controller is replaced with fuzzy logic controller.

# 8. References

- [1]. P. Cortes, G. Ortiz, J. Yuz, J. Rodriguez, S. Vazquez, and L. Franquelo, "Model prescient control of an inverter with yield LC channel for UPS applications, "IEEE Trans. Ind. Electron., vol. 56, no. 6, pp. 1875–1883, Jun. 2009.

- [2]. R. Vargas, P. Cortes, U. Ammann, J. Rodriguez, and J. Pontt, "Prescient control of a three-stage nonpartisan point-clipped inverter, "IEEE Trans. Ind. Electron., vol. 54, no. 5, pp. 2697–2705, Oct. 2007.

- [3]. P. Cortes, A. Wilson, S. Kouro, J. Rodriguez, and H. Abu-Rub, "Show prescient control of multilevel fell H-connect inverters, "IEEE Trans. Ind. Electron., vol. 57, no. 8, pp. 2691–2699, Aug. 2010.

- [4]. P. Lezana, R. Aguilera, and D. Quevedo, "Display prescient control of an unbalanced flying capacitor converter, "IEEE Trans. Ind. Electron., vol. 56, no. 6, pp. 1839–1846, Jun. 2009.

- [5]. P. Correa, J. Rodriguez, I. Lizama, and D. Andler, "A prescient control conspire for current-source rectifiers, "IEEE Trans. Ind. Electron., vol. 56, no. 5, pp. 1813–1815, May 2009.

- [6]. M. Rivera, J. Rodriguez, B. Wu, J. Espinoza, and C. Rojas, "Current control for an aberrant grid converter with channel reverberation moderation," IEEE Trans. Ind. Electron., vol. 59, no. 1, pp. 7179, Jan. 2012.

- [7]. P. Correa, M. Pacas, and J. Rodriguez, "Prescient torque control for inverter-sustained enlistment machines, "IEEE Trans. Ind. Electron., vol. 54, no. 2, pp. 1073–1079, Apr. 2007.

- [8]. M. Odavic, V. Biagini, P. Zanchetta, M. Sumner, and M. Degano, "One example period ahead prescient current control for superior dynamic shunt control channels, "Power Electronics, IET, vol. 4, no. 4, pp. 414–423, Apr. 2011.

- [9]. D. Quevedo, R. Aguilera, M. Perez, P. Cortes, and R. Lizana, "Show prescient control of an AFE rectifier with dynamic references, "IEEE Trans. Power Electron., vol. 27, no. 7, pp. 3128–3136, Jul. 2012.

- [10]. Z. Shen, X. Chang, W. Wang, X. Tan, N. Yan, and H. Min, "Prescient advanced current control of single-inductor various yield converters in CCM with low cross direction, "IEEE Trans. Power Electron., vol. 27, no. 4, pp. 1917–1925, Apr. 2012.

#### **Author's Profile**

**Mr. Uppudi Saikumar** Received the B.Tech degree in Electrical and Electronics Engineering from DJR Institute of Engineering & technology, India and at present Pursuing M.Techwith the specialization of Power Electronics Drives in Laki Reddy Bali Reddy College of Engineering, Mylavaram.

**Mr.J.V. PavanChand**graduated in EEE from JNT University Hyderabad in 2004.He received M.Tech degree in the stream of Power Electronics in JNT University Kakinada in 2012and at present Pursuing Ph.D with the Specialization of Wind Turbine Interconnected to Grid in Vellore University, Vellore and presently working as Senior Assistant Professor in Lakireddy Bali Reddy College of Engineering, Mylavaram.